Giornata IU.NET 21/22 Settembre 2017

E-LAB, EPARTMENT OF IFORMATION INCERSITY OF PADOVA

# Galliun Nitride power devices: status, challenges and future opportunities.

**Gaudenzio Meneghesso**

University of Padova, Department of Information Engineering, via Gradenigo 6/B, 35131 Padova, Italy gaudenzio.meneghesso@unipd.it

### Why GaN-based devices

**ECPE Position Paper:** Today already 40% of the world wide used energy is provided by electric power. It is expected that this share is going to rise to about 60% until 2040. This enormous amount of energy not only needs to be produced environmentally friendly, but it also should be distributed and used efficiently.

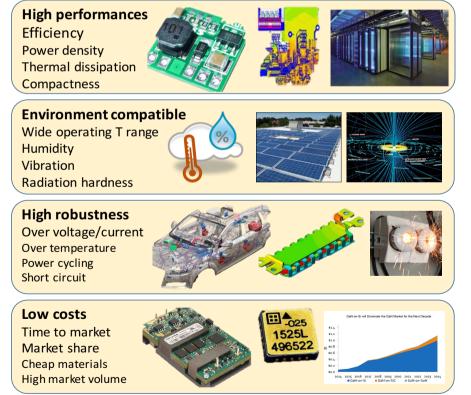

#### **Challenging Requirements of Power Electronics**

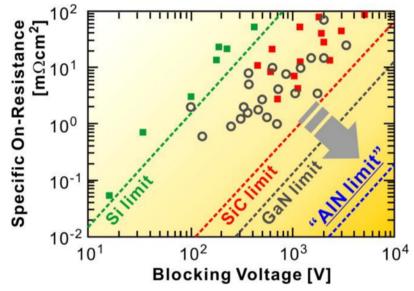

Wide Bandgap Semiconductors (WBG) such as **SiC, GaN, AIN and diamond** show superior material properties compared to Silicon. Due to these unique characteristics (high maximum current, high breakdown voltage, and high switching frequency), these WBG represent the unique material of choice to help solving the energy problems of the future.

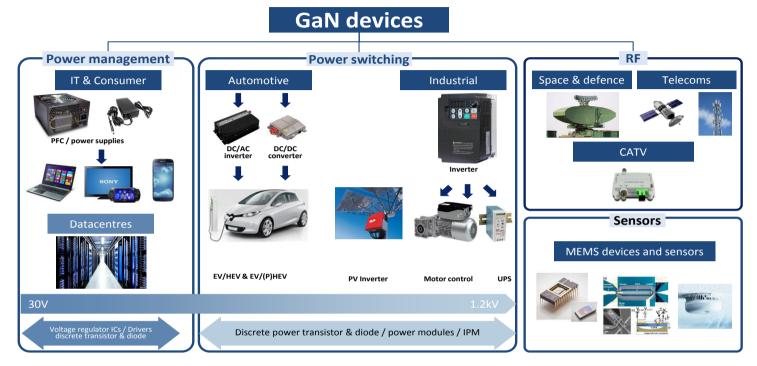

# **Opportunities of GaN technology**

Energy saving is clearly stated in the **SET-PLAN document**. Over 50% of all consumed energy in the world is electrical, and about 60% of all electrical energy is lost due to the many (inefficient) conversion steps (AC do DC, different voltage levels) which are required to bring the electricity from its source to the consumer. Semiconductor devices in general can greatly help to increase the efficiency of the power converters. **The adoption of WBG materials in power electronics is a key factor to reach higher energy efficiency and reducing power management losses**.

http://ec.europa.eu/energy/en/topics/technology-and-innovation/strategic-energy-technology-plan

# Why GaN-based devices

#### GaN devices offer five key characteristics:

- high dielectric strength,

- high operating temperature,

- high current density, ۲

- high speed switching

- low on-resistance. •

#### **Technical advantages of GaN-Based electronics:**

- Higher efficiency; ٠

- Reduced heat sink requirements

- 80% reduction in system volume and weight ٠

- Lower voltage drop for unipolar devices

- Increased output power •

- Improved transient characteristics and switching speed

- Reduced electrical noise from smaller system packages

- Reduced electrical noise due to virtually zero recovery charge

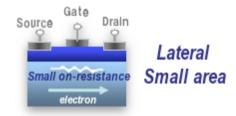

GaN

Vertical

Source

SI MOS Transistor Gate

Source

Large

onresistance

Drain

### **Opportunities of GaN technology**

#### What?

- 100V and 600V

Enhancement (E) mode

GaN HEMT

- Single chip, normOFF transistor

- > Robust, reliable P-Gate concept

- Fastest normOFF concept available

- Can be tailored for high efficiency or high frequency operation

- Key for integration at chip and/or package level

#### How?

EMode **600V**, **DSO-20**: sampling prototypes with NDA

#### Bottom/Top side Cooling

Emode 600V, TOLL: sampling prototypes with NDA

Low profile, small footprint

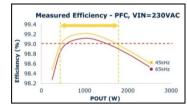

#### Why?

Efficiency: very high efficient SMPS

- Highest efficiency PFC

- > Density: very compact SMPS

Ultra-thin SMPS

9mm

#### Where?

Example: >2.5kW SMPS in where op. cost matters

Data centers

> Example: OLED TV or other 200-800W SMPS

Ultra-thin TV

#### **100V-200V Emode GaN for Efficiency and Density**

Courtesy of Steve Stoffels (imec)

### **Open Issues in GaN: 1) Substrates**

|                          | GaN Templates                                                            | Low Defect GaN templates (ELO)                                                                               | Freestanding<br>GaN                                                            | Engineered<br>Substrate                                                                    | GaN boule<br>("Bulk GaN")                                        |

|--------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Description              | 10- 250 µm thick<br>GaN layer on a<br>hetero substrate<br>(sapphire, Si) | 10-250 μm thick GaN<br>layer on hetero<br>substrate with low<br>dislocation density<br>areas obtained by ELO | 300-500 µm thick<br>GaN layer separated<br>from a mother<br>substrate.         | Carter substrate<br>Thin GaN layer from<br>GaN wafer bonded<br>onto a carrier<br>substrate | GaN single crystals sliced into wafers                           |

| TD density               | 7x10 <sup>x</sup> to 6x10 <sup>x</sup>                                   | < 1x10 <sup>×</sup> in low defect<br>are as                                                                  | 1x10 <sup>×</sup> to 5x10 <sup>×</sup><br>Depending on<br>method               | Depends on original<br>GaN wafer                                                           | 1x10 <sup>x</sup> to 5x10 <sup>x</sup><br>Depending on<br>method |

| Benefits                 | Relatively low cost,<br>large diameter<br>available (4")                 | LD manufacturing<br>possible in low TD<br>areas                                                              | Low TD,<br>homogenous with<br><u>some techniques</u> . Up<br>to 4-6" available | Low cost: one GaN<br>wafer can lead to xx-<br>yy engineered<br>wafers.                     | Very low TD                                                      |

| Drawback                 | TD density too high<br>for LD and UHB-<br>LED, wafer bow                 | TD not homogeneous<br>across surface, wafer<br>bow                                                           | Cost                                                                           | Thermo-mechanical<br>performance driven<br>by carrier                                      | Cost, dimensions<br>Availability                                 |

| Possible<br>Applications | R&D, possible future<br>in HB-LED*                                       | LD, R&D                                                                                                      | LD, UHB-LED, HB<br>LED, Power                                                  | LD, UHB-LED, HB<br>LED, Power, RF                                                          | High performance<br>devices: LD, UHB-<br>LED, Power              |

GaN HEMTs - G. Meneghesso- Giornata IU.NET - 21 Settembre 2017 6

UNIVERSITY OF PADOVA

CITAN

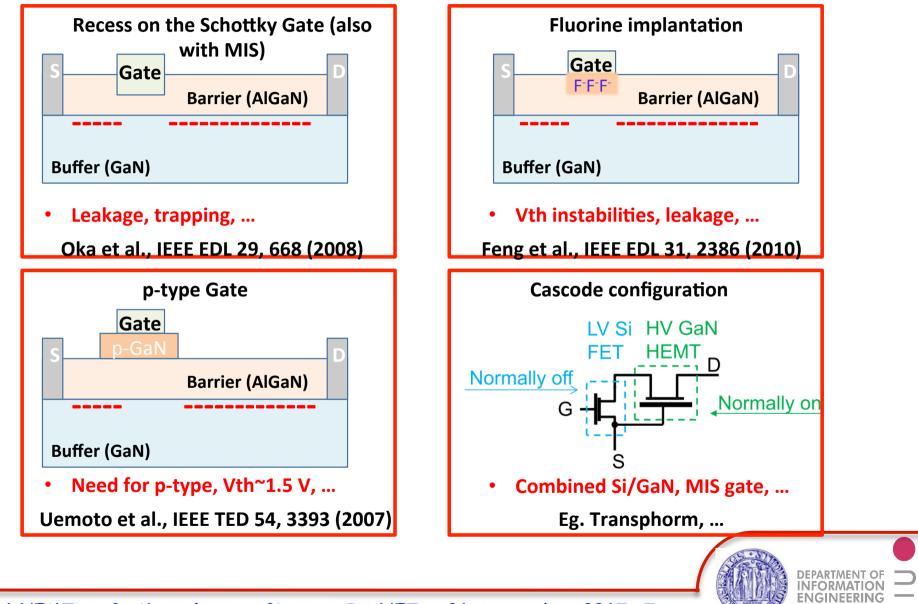

### Open Issues in GaN: 2) e-mode

GaN HEMTs - G. Meneghesso- Giornata IU.NET - 21 Settembre 2017 7

UNIVERSITY OF PADOVA

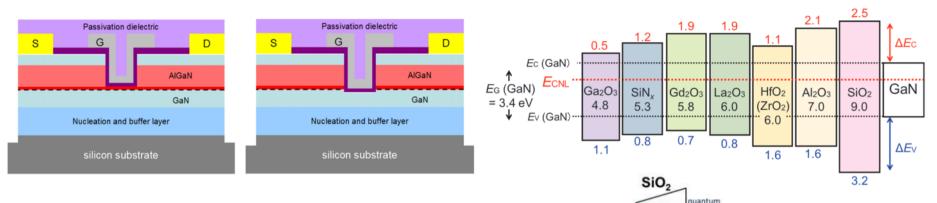

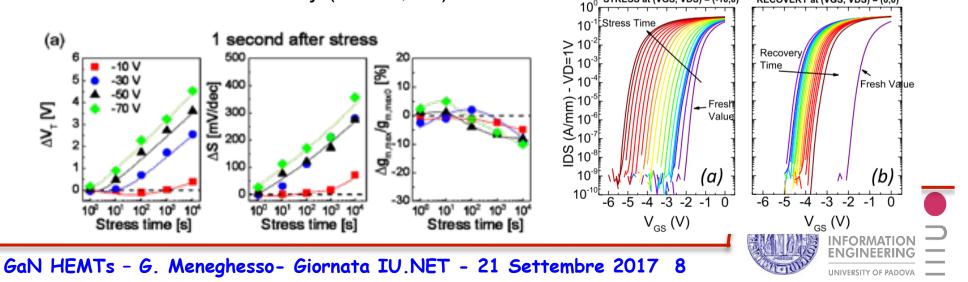

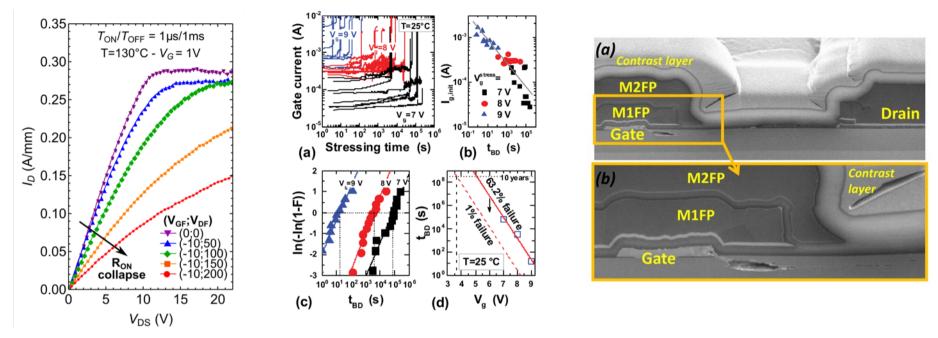

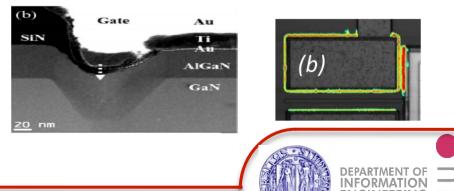

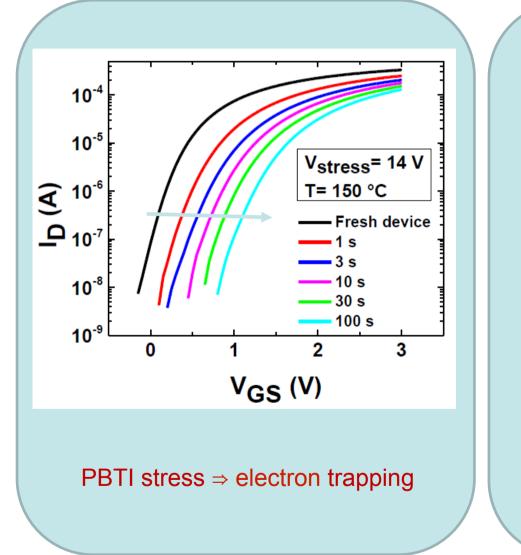

### Open Issues in GaN : 3) MIS/MOS

ide defects

VX

interface

defects

STRESS at (VGS, VDS) = (-10,0)

metal

GaN

channel

RECOVERY at (VGS, VDS) = (0.0)

leakage

GaN/AIGaN

barrier

#### Issues:

- Very complex structure

- Weak e-mode (Vth 1-2 V)

- Traps/defects in bulk and interfaces → Vth instabilities (PBTI, NBTI, ...)

- Oxide/Insulator stability (TDDB, ....)

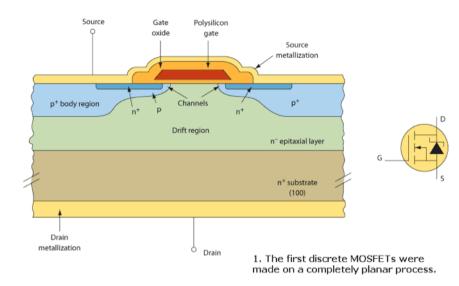

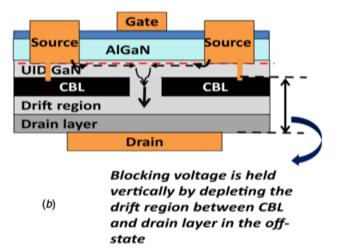

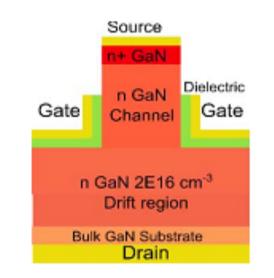

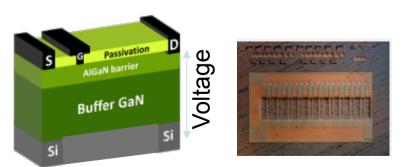

### **Open Issues in GaN: 4) Vertical**

- All Si power devices are Vertical

- Is this mandatory also for GaN? (Power community want them)

- Need very good bulk GaN supplier!!

- If we get out from 2DEG, is GaN still valuable?

- The electrical properties of Bulk-GaN is not far from the SiC, then why GaN?

- The best compromise today is the vertical Fin (proposed by Palacios, MIT)

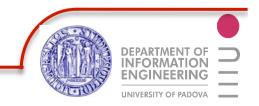

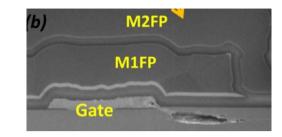

#### Open Issues in GaN: 5) Parasitic & Reliability

#### Today's major issues:

- Trapping phenomena; mainly determined by the substrate (C, Fe compensation)

- Degradation (Failure) modes and mechanisms, not fully understood

- MIS/MOS → TDDB and Vth instability

- p-GaN gate → max positive gate bias

- The D-Mode devices (with Thin insulating layer at GaN) have demonstrated good reliability, but the cascode solution is not wanted;

- The qualification procedure has not been yet standardize (large effort in the GaN community)

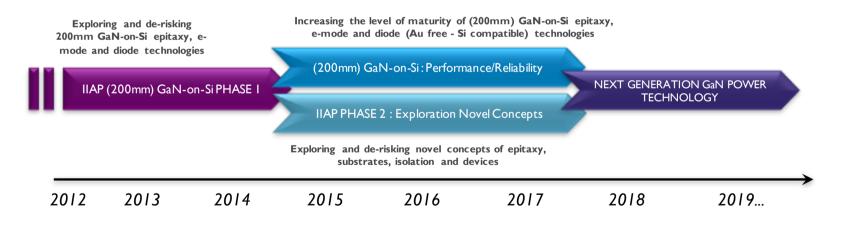

E2COGaN targeted the demonstration of **GaN-on-Si as a disruptive high voltage** (HV) technology and High Electron Mobility Transistors through the whole value chain up to demonstrators with high industrial, societal and environmental relevance. Aims are higher efficiency, higher switching frequency, smaller footprint and weight and competitive cost on system level.

- E2CoGaN (and Hiposwitch) gave a great burst to the European GaN technology development, thanks to the involvement of all major European Players.

- Devices performances and stability greatly improved during the project

- Packaging and demonstrators have also been developed

- IUNET Contributors:

- Padova

- Bologna

- Modena e Reggio Emilia

- Calabria

### **IU.NET in GaN Projects**

The H2020 NEREID project is a Coordination and Support Action (n° 685559) entitled "NanoElectronics Roadmap for Europe: Identification and Dissemination"

The objective of this project is to elaborate a new **Roadmap for Nanoelectronics** and for the advanced concepts developed by Research Centres and Universities in order to achieve an early identification of promising novel technologies, and cover the R&D needs all along the innovation chain.

IU.NET is involved with UniPD (Gaudenzio Meneghesso) Task 4.3 Smart Power devices (GaN, SiC ...)

# **IU.NET in GaN Projects**

#### InRel NPower

Si MOSFET = 4H-SiC MOSFET O GaN HEMT

- GaN-on-Si (the current standard) → The project's baseline technology, with an emphasis on improving reliability by using different epitaxial buffer structures

- Innovative device architectures based on substrate removal to increase the maximum operating voltage

- AIN-based electronics → Explorative investigation of the epitaxy of Ultra-Wide Bandgap layer structures grown on AIN templates (obtained by HVPE or 3SG ) or bulk substrates (grown by PVT)

- Advanced Material Characterization → A major objective is to determine the correlation between material properties and device performance through XRD, AFM, SEM, TEM, CL, PL, EBSD, …

## GaN expertiese in IU.NET - UniPD

#### **Research topics:**

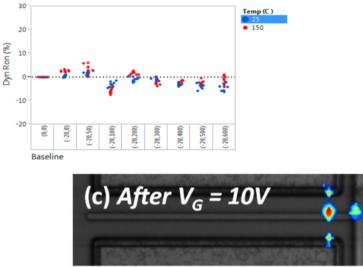

- Reliability of GaN HEMTs with Schottkygated structure → Identification of failure mechanisms, analysis of dominant trapping processes

- Charge-trapping issues in 650V GaN MIS-HEMTs for efficient power conversion. Total suppression of dynamic Ron

- Study of the degradation processes of transistors with p-GaN gate submitted to accelerated lifetest

- Study of the reliability of RF transistors for wide band/power transmission based on Ga

- Reliability and stability of vertical GaNbased transistors for power applications

- Time-dependent buffer degradation processes, dependence on epitaxial parameters and device geometry

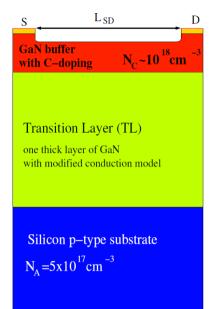

### GaN expertiese in IU.NET - UniBO

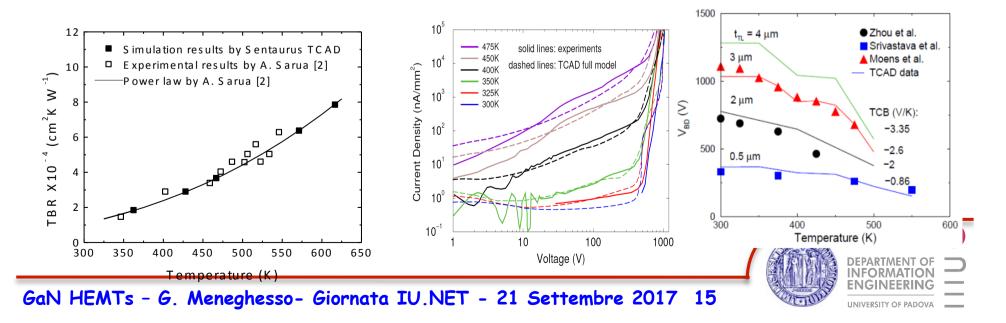

#### Largely improved TCAD simulation setup:

New impact-ionization model, new approach to account for the role of transition layers and thermal boundary resistance (TBR).

#### Role of traps in the buffer and at the interface:

TCAD results with traps correlated with experiments on vertical and lateral structures

#### **Explanation of buffer breakdown vs. T:**

Electron and hole impact-ionization generation + Poole-Frenkel mobility in the transition layer.

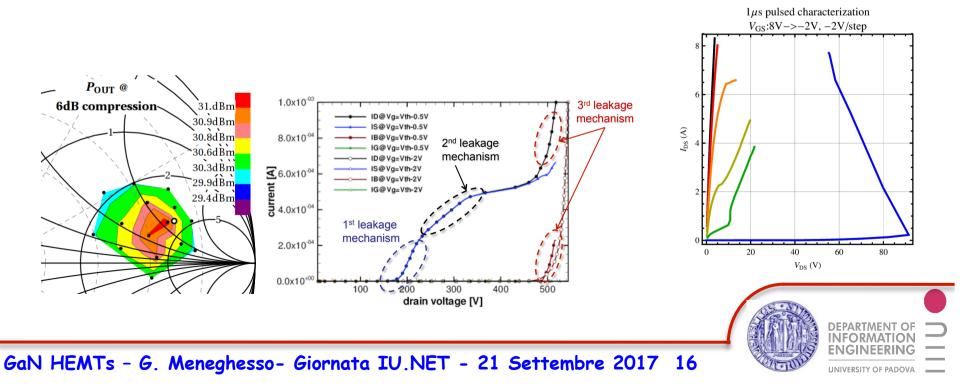

### GaN expertiese in IU.NET - UNIMORE

- Activities:

- numerical simulation of trap-related effects, degradation mechanisms, and breakdown effects in GaN HEMTs for RF and power switching applications.

- numerical simulation of GaN blue LEDs.

- Recent collaborations/funding: Univ. Padova, Politecnico di Torino, MIT, Leonardo (Finmeccanica), Infineon, ESA.

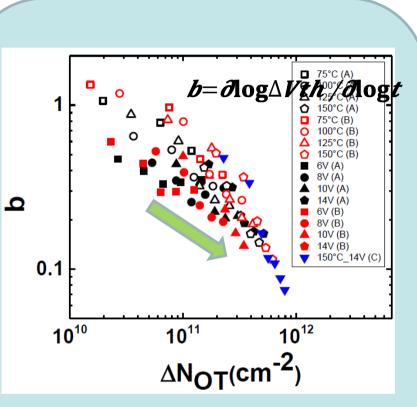

### GaN expertiese in IU.NET: UniCAL

Trapping rate parameter b versus trapped charges exhibits a universal decreasing behavior independently of stress time, stress voltage, stress temperature, and device-todevice variability

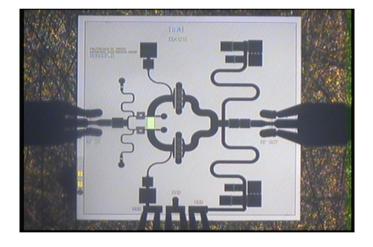

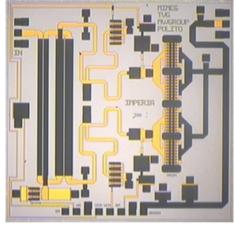

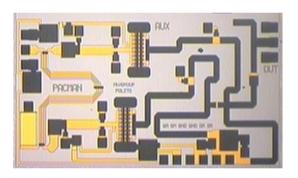

# GaN expertiese in IU.NET - PoliTO

- Characterization and modeling at device level widely exploited for technology assessment (EU KORRIGAN Project) since 2007

- GaN technology investigated with the design of specific demonstrators both hybrid and in MMIC feature with the major research-commercial foundry (Wolfspeed, Qorvo, UMS,OMMIC)

- Design of HPA for Ericsson, Qorvo, Huawei → Backhaul (7-15 GHz) linear and Doherty PAs

15 GHz 4 W Doherty Power Amplifier 2016

7 GHz 5 W linear (class AB) Power Amplifier 2014

7 GHz 10 W reconfigurable Doherty Power Amplifier 2015

### GaN expertiese in IU.NET - UniPI

Understanding the substrate leakage current in GaN-on-Si FETs (1 of 2) 10 10 30°C Current density (A/mm<sup>2</sup>) 25°C  $10^{-1}$ Current density (A/mm<sup>2</sup>) 50°C 10 50°C GaN 70°C 75°C 10-3 90°C 10-5 100°C – 110°C 125°C 10-TL 10 - 130°C - 150°C TL 10-5 – 150°C AIN AIN 10-7 10-6 Measured Si Si Simulated 10 10-7 TL (b) Full epi 10 10-6 (a) 10<sup>-10</sup> 10-750 1000 250 500 150 200 250 0 50 100 Voltage (V) Voltage (V) Interrupted runs Leakage current of the Leakage current of the with only the Full epi layer **Transition layer** transition layer (TL) have been fabricated in order FN SRH to understand the p-Si impact of the Si substrate on the leakage current (d) DEPARTMENT O

GaN HEMTs - G. Meneghesso- Giornata IU.NET - 21 Settembre 2017 19

UNIVERSITY OF PADOVA

INFORMATION ENGINEERING